ANSI SCTE 233 pdf free download

ANSI SCTE 233 pdf free download.Wavelength-Division Multiplex Small Form Factor Pluggable (PXFP- WDM) Optical Transmitter Module Interface Specification.

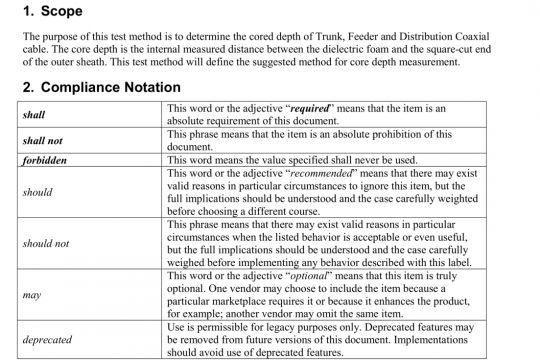

6. Management Interface

2-Wire Communications (PC) for the PXFP-WDM module are based upon IXFP MSAI. 12C is an implementation of the NXP (formerly Philips) 12C IUM 102041 specification with mapped memory address locations (also known as “well-known addresses”) for diagnostics and operations. The SFF Committee specifies the PC common memory mapping in [XFP MSAJ and [SFF-8477j for SFP and XFP, as well as additional physical layer requirements. This specification uses the same well-known memory map locations (addresses) for functions that are the same or substantially similar. Some memory map fields from [XFP MSAJ and [SFF-8477] are re-allocated or not used; in addition, some memory map fields have been added.

The PXFP-WDM module shall implement the 12C requirements specified in LXFP MSAI, except where specified differently in the following sections.

6.1. Summary of 2-Wire Communications Requirements

In [XFP MSA] 2-wire communication requirements are spread across several sections, including Section

4.2 and Table 26, Section 2.6 and Table 3. The following bullets summarize the requirements in IXFP

MSAI; refer to [XFP MSA] for complete details.

• PC communications may not be available for up to 300 ms after power up or reset

• The 12C interface bus of the PXFP-WDM module is not a shared one, in contrast to that of the XFP module, as it does not have a Mod_DeSel pin.

• There must be at least 20 jis between the STOP signal and the next START signal for a particular module.

• The clock rate can be as high as 400 kHz (PC fast mode).

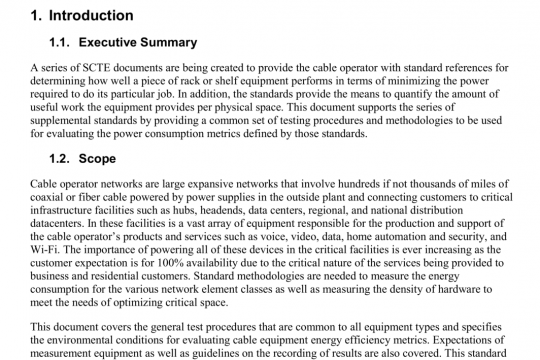

6.2.1. PXFP-WDM Module Boot Up Sequence When a PXFP-WDM module is plugged in, the host needs to perform a number of initialization steps in a particular order with a particular timing. Some of these involve the PXFP-WDM module pins and some involve IPC communications. As most of these are documented in the [XFP MSA] or are implied by stated dependencies, a reference to the location(s) in that document will accompany each step in the following sequence descriptions. Before the boot up sequence can be discussed, communications and host requirements need to be understood. 6.2.1.1. I?C Communications Requirements Once IC is operational, the host shall adhere to the timing requirements defined in Section 4.2, Table 26 of [XFP MSA]. Write operations may cause the PXFP-WDM module to not respond to further IFC signals or messages for up to 40 ms (twe in Section 4.3, Table 27, and Section 4.5.7 of [XFP MSA]). The specification does not restrict this to EEPROM writes. This applies for writes from one to four bytes (the limit for a write is four bytes). The PXFP-WDM module may perform a clock stretch of up to 500 μs during read or write operations (T_ clock_ hold, [XFP MSA] Section 4.3, Table 27). This is distinct from unresponsiveness after a write operation (twn). 6.2.1.2. Pin State Prior to PXFP-WDM Module Boot Up Before a PXFP-WDM module can begin boot up, the host shall meet the following pin requirements. The voltages listed for pins 6 (VCC5), 8 (VCC3_ _Tx), and 9 (VCC3_ Rx) in Table 4 shall be available.ANSI SCTE 233 pdf download.